|

|

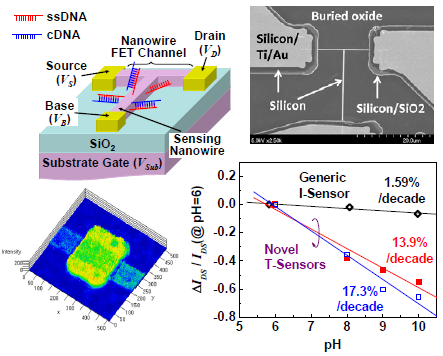

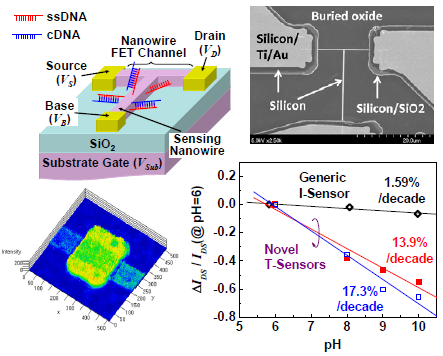

This is a rapidly growing, interdisciplinary field of research field spanning across nanoscience, medical therapy, and disease diagnostics. The advances in understanding and manipulation of nanoscale scientific phenomena have indeed offered unprecedented opportunities and capabilities to address timely medical and biological problems. Our grand research mission is to develop very low-cost and high impact disease diagnostic platforms for deployment at the point-of-care (POC). The criteria on the signal transduction device technology include superior sensitivity, multiplex and simple operations, response timeliness, compactness, reusability, simple fabrication, and electronic interfaces. As a contending POC diagnostic platform component technology, semiconductor nanowire FET sensors permit visual-label-free and real-time electronic detections of numerous charged biomarkers with high sensitivity and great selectivity. These detection sensitivity and selectivity need, however, to be further improved to meet the POC diagnostic requirements.

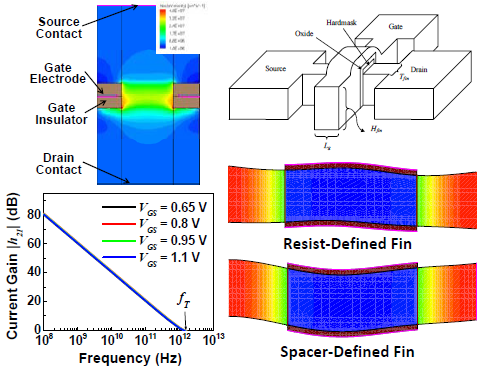

While many pioneering research efforts have been focusing on either the development of nanowire material and fabrication, or detection of unconventional biomolecules, nanoDTL exploits the fundamental scientific principles and engineering measures to maximize the detection sensitivity and selectivity. Selected specific research directions include: (i) exploring the fundamental relationships between voltage biasing, analyte type, and counter ion strength, (ii) formulation of inventive voltage biasing schemes, and (iii) development of transformative nanowire FET biosensor structures. To ensure our scientific research accomplishments can be translated into practical medical devices, we have maintained experimental collaborations with colleagues at Molecular and Medical Pharmacology, Center for Small Bowel Diseases, and others in our top-ranking School of Medicine at UCLA.

|